According to the news from the School of Microelectronics of Fudan University, Zhou Peng’s team of the school has verified the double-layer channel thickness of 0.6 / 1.2 nanometers for the 3-5 nanometer node transistor technology. Gate All Around (GAA), which realizes the integration of high drive current and low leakage current, provides a new technical approach for the development of high-performance and low-power Electronic devices.

It is reported that the relevant results have been published online at the 66th IEDM International Conference on Electronic Devices.

The report mentioned that after the process process is upgraded to below the 5nm node, it is difficult to continue to improve the performance of traditional transistor scaling, and major innovations are required. So GAA transistors take advantage of the potential, which can achieve better gate control and leakage control.

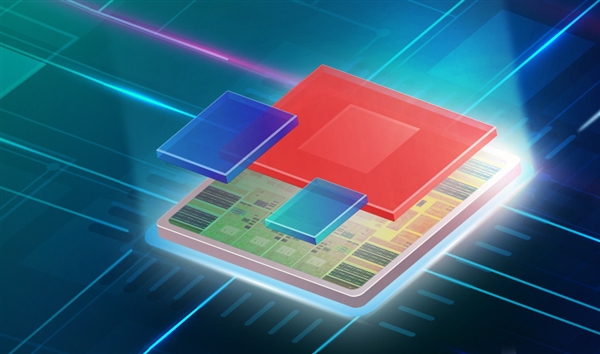

This time, Zhou Peng’s team designed and fabricated an ultra-thin gate-surrounded double-bridge-channel transistor. Compared with ordinary MoS2 transistors, the driving current is increased by more than 400%, and the ideal sub-threshold swing (60mV/dec) can be achieved at room temperature. decreased by two orders of magnitude.

It is reported that the GAA transistor is also translated as “surround gate transistor”, replacing the FinFET (fin field effect transistor) developed by the team of Chinese professor Hu Zhengming. According to the information currently available, Samsung intends to introduce GAA transistors from the first generation of 3nm that will be put into production in 2022. TSMC is slightly conservative, 3nm is still FinFET, and 2nm starts to enable GAA.

In addition, Liang Mengsong of SMIC also disclosed a few days ago that the company’s 8 most critical and most difficult technologies of 5nm and 3nm have also been launched in an orderly manner. As long as the EUV lithography machine arrives, it can enter the comprehensive development stage.

Schematic diagram of double-bridge channel transistor and its performance graph