Summary

The purpose of developing the serial interface industry standard JESD204A/JESD204B is to solve the problem of interconnecting the latest broadband data converters with other system ICs in an efficient and cost-effective manner. The motivation is to standardize the interface through the use of an adjustable high-speed serial interface to reduce the number of digital input/output between the data converter and other devices (such as field programmable gate array FPGA and system-on-chip SoC).

Trends show that the latest applications, as well as the upgrade of existing applications, are constantly demanding broadband data converters with higher sampling frequencies and data resolutions. The transmission and acquisition of data to these broadband converters exposes a very big design problem, that is, the bandwidth limitation of the existing I/O technology causes the number of pins used by converter products to be more.The result isPCB designAs the interconnect density increases, it becomes more complicated. The challenge is to control electrical noise while carrying a large number of high-speed data signal traces, as well as the ability to provide GSPS-level broadband data converter sampling frequency, use fewer interconnections, simplify PCB layout problems, and achieve smaller size without Decrease overall system performance.

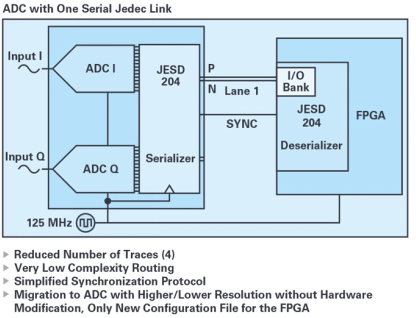

Market forces continue to put pressure on a given system to have more features and functions and better performance, driving the demand for higher data processing capabilities. High-speed analog-to-digital converters and digital-to-analog converters to FPGA interfaces have become limiting factors for certain system OEMs to meet the needs of next-generation massive data processing. The JESD204B serial interface specification was established specifically to solve this critical data link problem. Figure 1 shows a typical high-speed converter to FPGA interconnect configuration using JESD204A/JESD204B.

The rest of this article will discuss some of the key end-system applications that drive the development of the specification, as well as the comparison of serial low-voltage differential signaling (LVDS) and JESD204B.

figure 1. Typical high-speed converter to FGPA interconnect configuration using JESD204A/JESD204B interface (source: xilinx®).

Application drives demand for JESD204B

Wireless infrastructure transceiver

At present, wireless infrastructure transceivers use OFDM-based technologies such as LTE. This type of technology uses DSP Modules deployed with FPGA or SoC devices to drive antenna array elements to individually generate beams for each user’s mobile phone. In transmit and receive modes, each array element may need to transmit hundreds of megabytes of data per second between the FPGA and the data converter.

Software defined radio

Today’s software-defined radio technology utilizes advanced modulation schemes, can be reconfigured in real time, and greatly increases the channel bandwidth to provide the best wireless data rate. The high-efficiency, low-power, low-pin count FPGA-to-data converter interface in the antenna path plays a decisive role in performance. The software-defined radio architecture has been integrated with the transceiver infrastructure for multi-carrier, multi-mode wireless networks, supporting GSM, EDGE, W-CDMA, LTE, CDMA2000, WiMAX and TD-SCDMA.

Medical imaging system

Medical imaging systems include ultrasound,computerTomography (CT) scanners, magnetic resonance imaging (MRI), etc., these applications generate many channels of data, which flow through the data converter to the FPGA or DSP. The continuous increase in the number of I/O channels requires the use of interposers to match the pin outputs of FPGAs and converters, forcing an increase in the number of components and complicating the PCB. This increases the cost and complexity of the client system; these problems can be solved by using a more effective JESD204B interface.

Radar and safety communications

The pulse structure of current advanced radar receivers is becoming increasingly complex, forcing the signal bandwidth to rise to 1 GHz or higher. The latest active electronically adjusted array (AESA) radar system may contain thousands of components. The high-bandwidth SERDES serial interface is used to connect the array element data converter and FPGA or DSP, process the received data stream, and send the processed data stream.

Choose between serial LVDS and JESD204B interface

In order to make the best choice between converter products that use LVDS and multiple versions of the JESD204 serial interface specification, it is useful to compare the features and functions of each interface. Table 1 compares the interface standards in a simple tabular form. At the SERDES level, the significant difference between LVDS and JESD204 is the channel data rate. The serial link rate per channel supported by JESD204 is more than three times that of LVDS. When comparing advanced functions such as multi-device synchronization, deterministic delay, and harmonic clocking, JESD204B is the only interface that provides these functions. All channels and channels are sensitive to certain delays and require wide-bandwidth multi-channel converters, which will not be able to effectively use LVDS or parallel CMOS.

Table 1.Serial LVDS and JESD204 specification comparison

LVDS overview

LVDS is the traditional method of connecting data converters with FPGA or DSP. LVDS was released in 1994 with the goal of providing higher bandwidth and lower power consumption than the existing RS-422 and RS-485 differential transmission standards. With the release of TIA/EIA-644 in 1995, LVDS became the standard. In the late 1990s, the utilization rate of LVDS increased, and with the release of TIA/EIA-644-A in 2001, the LVDS standard also issued a revised version.

LVDS uses differential signals with low voltage swings for high-speed data transmission. The typical value of the current driven by the transmitter is ±3.5 mA, passing 100 ΩresistanceThe logic level with matching polarity is sent, and a voltage swing of ±350 mV is generated at the receiver end. The current is always conducting and is routed to different directions to produce logic 1 and logic 0. The always-on feature of LVDS helps to suppress synchronous switching noise spikes and potential electromagnetic interference-in single-ended technology, the switching action of the transistor may generate these noise and interference. The feature of LVDS differential also provides effective suppression against common mode noise sources. Although in an ideal transmission medium, the standard predicts that the rate may exceed 1. 9 Gbps, the maximum data rate recommended by the TIA/EIA-644-A standard is 655 Mbps.

The substantial increase in data channels and speeds between FPGAs or DSPs and data converters—especially the applications discussed above—has exposed some problems with the LVDS interface (see Figure 2). In reality, the bandwidth of the differential LVDS line is limited to around 1.0 Gbps. In many current applications, this limitation results in the need for many high-bandwidth PCB interconnections, and failures may occur everywhere. A large number of traces also increase the complexity or overall size of the PCB, leading to an increase in design and manufacturing costs. In some applications with huge bandwidth requirements, the data converter interface has become a limiting factor in meeting the required system performance.

figure 2. The system design and interconnection challenges brought by using parallel CMOS or LVDS.

JESD204B overview

The JESD204 data converter serial interface standard was established by JEDEC Solid State Technology Association JC-16 Interface Technical Committee. The goal is to provide a higher rate serial interface, increase bandwidth and reduce digital input and output between high-speed data converters and other devices. Number of channels. The basis of this standard is the 8b/10b coding technology developed by IBM, which does not require a frame clock and a data clock, and supports single-pair communication at a higher rate.

In 2006, JEDEC released the JESD204 specification, enabling the rate on a single data channel to reach 3.125 Gbps. The JESD204 interface is self-synchronizing, so there is no need to calibrate the PCB wiring length to avoid clock skew. JESD204 relies on the SERDES ports provided by many FPGAs in order to release general-purpose I/O.

JESD204A was released in 2008 and added support for multiple data channels with consistent timing and channel synchronization. This enhancement makes it possible to use higher bandwidth data converters and multiple simultaneous data converter channels, and is particularly important for wireless infrastructure transceivers used in cellular base stations. JESD204A also provides multi-device synchronization support, which is beneficial to applications that use a large number of ADCs such as medical imaging systems.

JESD204B is the third revision of the specification, which increases the maximum channel rate to 12. 5 Gbps. JESD204B also adds support for determining the delay, which enables the communication of synchronization status between the receiver and the transmitter. JESD204B also supports harmonic clocks, making it possible to obtain high-speed data converter clocks from low-speed input clocks based on the determined phase.

in conclusion

The JESD204B industrial serial interface standard reduces the number of digital input and output channels between high-speed data converters and FPGAs and other devices. Fewer interconnects can simplify layout and make it possible to achieve smaller size designs (see Figure 3). These advantages are important for many high-speed data converter applications, such as wireless infrastructure transceivers, software-defined radios, medical imaging systems, and radar and secure communications. ADI is a founding member of the JESD204 standards committee. At the same time, we have developed compatible data converter technologies and tools, and launched a comprehensive product roadmap. By providing customers with products that combine our advanced data converter technology and integrated JESD204A/JESD204B interfaces, we are expected to make full use of this major interface technology breakthrough to help customers solve system design problems.

image 3. JESD204 has high-speed serial I/O capability, which can solve the system PCB complexity challenge.

About the Author

George Diniz is the product line manager of Analog Devices’ High Speed Digital-to-Analog Converter Group (Greensboro, North Carolina). The development team he leads is responsible for the development of JESD204B receiver and transceiver interface cores for integration into high-speed analog-to-digital and digital-to-analog converter products.He owns 25 yearssemiconductorIndustry work experience, held various positions such as design engineering and product line management. Before joining ADI, George was a design engineer at IBM, where he was engaged in power PCprocessorMixed-signal design of custom SRAM macros, PLL and DLL functions. He holds a Master of Electrical Engineering (MSEE) from North Carolina State University and a Bachelor of Electrical Engineering (BSEE) from Manhattan College. In terms of entertainment, George likes outdoor activities, repairing cars and running.